XC3S200AN-4FTG256I每路大致的主程序是:检测到振铃信号后(即为振铃检测脚变低并保持8ms以上),继电器吸合,同时马上给机定盒回一接通信号——#键(保持 400ms)。然后等待机定盒发送点播信息:客房号、点播的节目号,共4位DTMF码;若1s内无DTMF码收到(收到表示为解码芯片的DV脚变高)表示操作有误,继电器断开,状态位复原,作业指针回0。收齐4位DTMF码后将其整理并带上该路的标志,转化成3字节送到串行发送缓冲区,在定时器中断服务程序中发送。等待视频服务器回送应答信息,根据应答信息不同向机定盒回送不同的信息;若超时无应答也向机定盒回送一码(发码时间都为100ms)。最后,继电器断开,状态标志复原,缓冲区清0,作业指针也回到0。一个过程完成。 2.作业流程 为了能实现8路分时工作,最主要的工作是将这一过程细分成一个个作业。笔者通过设计把它分成8个作业,各作业的流程如图2所示。 以上每一作业返回后,“路”指针自动加1,到8后回到0,以保证分时工作合理。

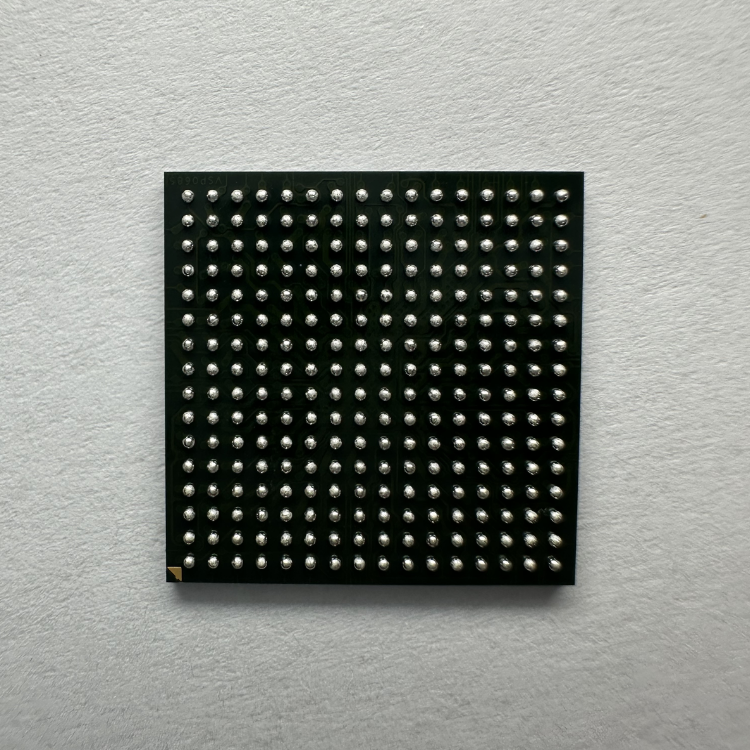

XC3S200AN-4FTG256I 规格

产品属性 属性值 选择属性

制造商: AMD

产品种类: FPGA - 现场可编程门阵列

RoHS: 详细信息

系列: XC3S200AN

逻辑元件数量: 4032 LE

自适应逻辑模块 - ALM: 1792 ALM

嵌入式内存: 288 kbit

输入/输出端数量: 195 I/O

电源电压-最小: 1.14 V

电源电压-最大: 1.26 V

最小工作温度: - 40 C

最大工作温度: + 100 C

数据速率: -

收发器数量: -

安装风格: SMD/SMT

封装 / 箱体: FBGA-256

商标: AMD / Xilinx

分布式RAM: 28 kbit

内嵌式块RAM - EBR: 288 kbit

最大工作频率: 250 MHz

湿度敏感性: Yes

栅极数量: 200000

工作电源电压: 1 V

产品类型: FPGA - Field Programmable Gate Array

1

子类别: Programmable Logic ICs

商标名: Spartan

单位重量:400 mg

XC3S200AN-4FTG256I由于电池容量增加到4000毫安时,Galaxy Z Flip 6的机身厚度较前代增加了7%,但充电功率依然维持在25W,这意味着续航虽然有所增加,但充电速度要比前代更慢一些。核心性能方面,Galaxy Z Flip 6将搭载骁龙8 Gen 3 For Galaxy移动平台,从Galaxy S24系列上同款芯片的性能表现来看,Z Flip 6的能耗控制、性能释放应该会有较好的平衡。

以往Galaxy Z Flip系列最大的问题就在于内存容量略小,即便是到了Galaxy Z Flip 5依然坚持使用8GB,且没有更大的版本可供选择。或许是考虑到AI功能需要更大的内存占用,Galaxy Z Flip 6终于也是提供了12GB内存版本,而存储空间依然以256GB起步。

XC3S200AN-4FTG256I作为小折叠屏,Galaxy Z Flip系列最大的优势还是轻巧便携,Galaxy Z Flip 6着重提升了性能、内存和显示尺寸,预计也能更好地结合Galaxy AI提供诸如智能翻译、AI搜索等功能。

DAVE——数字应用工程师,出自Infineon科技。它能帮我们准确而快速地进行基于Infineon8位、16位或32位单片机的嵌入式系统设计。由于Infineon的嵌入式控制器的寄存器的数量非常大,大约有一千多个。所以对大量寄存器的初始化是一件相当棘手的事,而有了DAVE的平台就能很轻松地完成这些事情。同时DAVE还可完成单片机的其它初始化工作,与Keil或、Tasking等编译软件实现链接,轻松完成嵌入式系统的软件开发工作。

XC3S200AN-4FTG256I是Infineon的16位微控制器XC2000家族中的一员,它将功能和性能都得到扩展的C166SV2内核、功能强大的片上外设子系统和各种片上存储器进行了完美结合。执行速度更快、稳定性更好、操作更简单。

XC3S200AN-4FTG256I单片机的时钟产生

XC3S200AN-4FTG256I单片机时钟产生单元(CGU)可非常灵活的产生单片机所需的时钟。通过锁相环(PLL),时钟产生单元(CGU)可将低频外部时钟转换为高频系统时钟,无需外部直接产生高频时钟。时钟产生单元(CGU)由时钟发生器和时钟控制单元(CCU)构成。

XC2336B单片机带有5 MHz的内部时钟源,可以在无外部时钟信号的情况下产生系统时钟(fsys)。该内部时钟源位于锁相环(PLL)单元中,通过对该单元的合理设置,即可完成该单片机的无晶振工作。但由此产生的系统时钟(fsys)受温度影响很大,时钟的精度不高,适合在简单的应用中使用。因此,常用的产生系统时钟 (fsys)的方法是,由高精度振荡器电路(OSC_HP)驱动一个外部晶振,产生的时钟信号送入锁相环(PLL)倍频后产生系统时钟(fsys)。振荡器电路包含一个反相放大器,以XTAL1为输入、XTAL2为输出。

在某些使用环境中,由于震动等原因,外部晶振有可能损坏。但是,在这种情况下,又不希望单片机处于死机状态,希望单片机能够发出一些报警信号,并能完成一些简单功能。那么,能否让单片机自动切换为内部时钟源工作呢?答案是肯定的。也就是要让单片机在正常状态下以高精度系统时钟运行,在外部晶振失效时以内部时钟源产生的系统时

钟运行,而且这两个系统时钟的值是一样的。

要完成XC3S200AN-4FTG256I外部与内部时钟源的切换,最主要的设置是对锁相环(PLL)的设置。因此我们先介绍一下XC2336B单片机的锁相环(PLL)。